什么是電容串擾?高速電子系統中的隱形干擾源

在當今技術飛速發展的時代,電子產品的設計正朝著高度集成化與高速化的方向邁進。隨著器件尺寸不斷縮小,數據傳輸速率卻持續攀升至新的量級。這一趨勢使得信號完整性(Signal Integrity, SI)問題日益凸顯,其中傳輸線間的串擾(Crosstalk)現象已成為高速電路設計中最具挑戰性的技術難題之一。

串擾的物理本質與電磁耦合機制

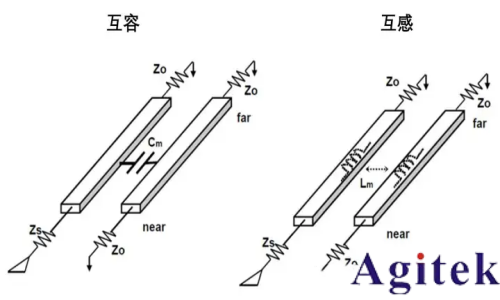

當高速信號在傳輸線中傳播時,信號路徑與其返回路徑之間會形成動態的電磁場分布。這種延伸至導體周圍的電磁場被稱為邊緣場(Fringing Field),其能量會通過互容(Mutual Capacitance)和互感(Mutual Inductance)兩種耦合機制,以電磁耦合的形式轉移到相鄰的傳輸線上。這種能量轉移現象即構成串擾的核心機制。

從電磁場理論視角分析,串擾本質上是傳輸線間通過電磁耦合實現的能量再分配過程。根據耦合路徑的差異,串擾可分為容性耦合與感性耦合兩種基本類型,二者在高速信號傳輸中往往同時存在并相互影響。

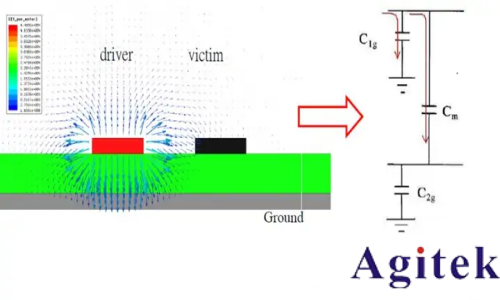

容性耦合:電場驅動的電壓干擾

互容的物理定義

互容(C?)是描述兩個導體間通過電場耦合強度的物理量,其定義為:當驅動線與被擾線之間存在單位電壓差時,兩導體間積累的電荷量。數學表達式為:

Cm=VQ

其中Q為耦合電荷量,V為驅動線電壓。

容性耦合機制

在時變信號作用下,驅動線的電壓變化(dV/dt)會在互容C?上產生位移電流,該電流通過被擾線的輸入阻抗形成感應電壓。這種電壓耦合效應在數字電路中表現為:

信號跳變沿引發的瞬態干擾

近端串擾(NEXT)中的容性分量

高阻抗節點處的顯著電壓擾動

容性耦合強度與以下因素密切相關:

導體間距:間距減小導致C?呈指數增長

介質常數:高介電常數材料增強電場耦合

平行走線長度:耦合能量隨長度線性增加

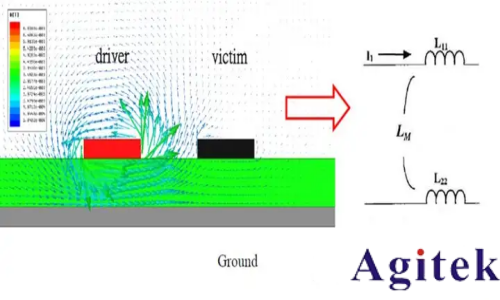

感性耦合:磁場誘導的電流干擾

互感的物理定義

互感(L?)表征兩個導體間通過磁場耦合的強度,其定義為:當驅動線中流過單位電流時,通過互感在被擾線中產生的磁通鏈數。數學表達式為:

Lm=IΨ

其中Ψ為磁通鏈,I為驅動線電流。

感性耦合機制

驅動線的時變電流(dI/dt)會產生變化的磁場,根據法拉第電磁感應定律,該磁場在被擾線中感應出電動勢,進而形成干擾電流。這種電流耦合效應在數字電路中表現為:

信號跳變沿引發的瞬態電流

遠端串擾(FEXT)中的感性分量

低阻抗回路中的顯著電流擾動

感性耦合強度受以下因素影響:

回路面積:增大回路面積顯著提升L?

導體間距:間距減小導致磁場耦合增強

信號頻率:高頻信號使dI/dt效應加劇

串擾的時域與頻域特性

在時域分析中,串擾表現為:

近端串擾(NEXT):干擾信號向信號源方向傳播

遠端串擾(FEXT):干擾信號向接收端方向傳播

脈沖展寬效應:導致信號邊沿速率下降

頻域分析揭示:

串擾幅度隨頻率升高而增大

容性耦合在高頻段占主導

感性耦合在中頻段更顯著

阻抗不連續點引發諧振增強

現代高速設計中的串擾控制策略

為有效抑制串擾,現代高速電路設計采用多維度控制技術:

空間隔離技術:

3W/5W布線規則(線間距≥3倍線寬)

差分對布線優化

防護走線(Guard Trace)應用

介質材料優化:

低介電常數(Dk)基板材料

嵌入式電容材料應用

均勻介質層設計

拓撲結構改進:

阻抗匹配網絡設計

端接電阻優化配置

飛線(Fly-by)拓撲應用

先進封裝技術:

硅通孔(TSV)三維集成

倒裝芯片(Flip Chip)封裝

嵌入式微帶線結構

電容串擾作為高速電子系統中的固有物理現象,其影響隨著信號速率的提升呈非線性增長。通過深入理解互容與互感的耦合機制,結合先進的電磁仿真工具與系統級設計方法,工程師能夠在納米級工藝節點下實現串擾的有效控制。未來,隨著人工智能輔助設計與新材料技術的突破,串擾抑制技術將持續演進,為5G/6G通信、人工智能計算等前沿領域提供可靠的信號完整性保障。

技術支持

關注官方微信

關注官方微信