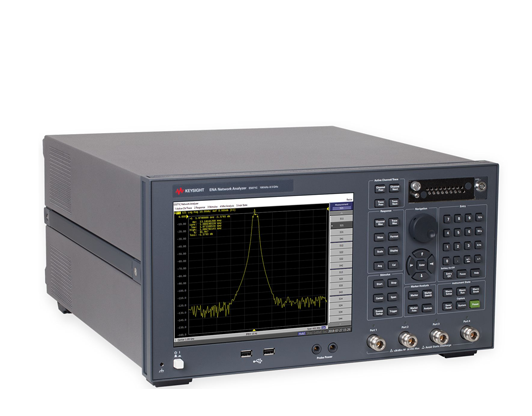

ADC采樣后數字信號突變的成因探究

ADC(Analog-to-Digital Converter,模擬數字轉換器)是連接模擬世界與數字系統的橋梁。自然界中的聲音、圖像、溫度等模擬信號,需經ADC轉換為數字信號(Q)后,才能在電子產品中進行處理、存儲或傳輸。

ADC技術演進與摩爾定律的驅動

1965年戈登·摩爾提出的“摩爾定律”指出,集成電路中晶體管密度將每兩年翻一番。這一預測持續推動著計算與模數轉換技術的飛躍式發展。FPGA與CPU性能的指數級提升,正是摩爾定律的直接體現。同時,ADC性能也受益于晶體管密度的增加,其采樣率與分辨率持續突破。

現代通信系統對ADC提出嚴苛要求:雷達與衛星通信帶寬已超2GHz,5G毫米波頻段更需支持2GHz以上帶寬。根據奈奎斯特采樣定律,采樣率需至少為信號帶寬的兩倍。數字中頻直接采樣技術的普及,進一步推高了對高速ADC芯片的性能需求。

高精度ADC的核心價值

高精度ADC通過以下機制提升系統性能:

更高采樣精度:準確測量模擬信號,適用于醫療儀器、測試測量等高精度場景。

更強噪聲抑制:提升信號質量,滿足音頻處理、圖像處理等對信噪比敏感的應用需求。

更大動態范圍:覆蓋信號幅度變化范圍,適用于重力測量、氣壓測量等寬范圍信號采集。

示波器ADC分辨率的量化分析

ADC位數決定垂直分辨率:n位ADC提供2?個量化電平(Q級)。

例如:

8位ADC:256 Q級,全量程800mV時分辨率3.125mV/電平

12位ADC:4096 Q級,相同量程下分辨率0.195mV/電平

量程設置對分辨率的影響:

波形占據屏幕1/2時,8位ADC實際有效位數降至7位

波形占據1/4時,有效位數進一步降至6位

滿屏顯示時,ADC分辨率得到充分利用

硬件限制與軟件放大:

傳統示波器在垂直刻度低于10mV/格時啟用軟件放大,此時分辨率不再提升。例如:

8位示波器在7mV/格設置下,硬件支持量程56mV,分辨率218μV

10位示波器在2mV/格設置下,支持滿帶寬,分辨率15.6μV(較8位提升14倍)

數字信號突變的潛在根源

ADC采樣后數字信號突變可能由以下因素導致:

量化誤差:低分辨率ADC導致信號細節丟失,尤其在信噪比不足時,低位數據易受噪聲干擾

量程設置不當:未充分利用ADC有效位數,如波形僅占屏幕小部分區域

前端噪聲耦合:示波器探頭與前端電路引入的噪聲超過ADC有效分辨率

采樣率不足:違反奈奎斯特定律導致頻譜混疊

非線性失真:ADC輸入緩沖器或采樣保持電路的非理想特性

優化建議

為獲取高質量數字信號:

選擇足夠位數的ADC(12位優于8位)

優化垂直刻度設置使波形滿屏顯示

使用低噪聲探頭與前端電路

確保采樣率≥2.5倍信號最高頻率

對關鍵信號采用過采樣與數字濾波技術

通過理解ADC工作原理與量化機制,工程師可有效診斷并解決數字信號突變問題,在高速數字系統中實現精確的信號采集與處理。

技術支持

關注官方微信

關注官方微信