高速 ADC技術的發展趨勢及測試方法

隨著數字信號處理技術和數字電路工作速度的提高,以及對于系統靈敏度等要求的不斷提高,對于高速、高精度的 ADC(Analog to Digital Converter)、DAC(Digital to Analog Converter)的指標都提出了很高的要求。比如在雷達和衛星通信中,所需要的信號帶寬已經達到了 2 GHz 以上,而下一代的 5G移動通信技術在使用毫米波頻段時也可能會用到 2 GHz 以上的信號帶寬。雖然有些場合(比如線性調頻雷達)可能采用頻段拼接的方式去實現高的帶寬,但是畢竟拼接的方式比較復雜,而且對于通信或其它復雜調制信號的傳輸也有很多限制。

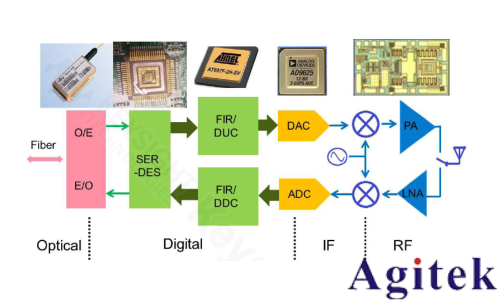

根據 Nyquist采樣定律,采樣率至少要是信號帶寬的 2 倍以上。同時為了支持靈活的制式、相控陣或大規模 MIMO 的波束賦形,現代的收發機模塊越來越普遍采用數字中頻直接采樣,這其實進一步提高了對于高速 ADC/DAC芯片的性能要求。下圖是一個典型的全數字雷達收發信機模塊的結構。

高速 ADC/DAC 在現代全數字雷達中的應用

可以看到,ADC/DAC 芯片是模擬域和數字域的邊界。一旦信號轉換到數字域,所有的信號都可以通過軟件算法進行處理和補償,而且這個處理過程通常不會引起額外的噪聲和信號失真,因此把 ADC/DAC 芯片前移、實現全數字化處理是現代通信、雷達技術的發展趨勢。

在全數字化的發展過程中,ADC/DAC 芯片需要采樣或者輸出越來越高的頻率、越來越高帶寬的信號。而在模擬到數字或者數字到模擬的轉換過程中造成的噪聲和信號失真通常是很難補償的,并且會對系統性能造成重大影響。所以,高速 ADC/DAC 芯片在采樣或者產生高頻信號時的性能對于系統指標至關重要。

目前在很多專用領域,使用的 ADC/DAC 的采樣率可以達到非常高的程度。比如 Fujitsu 公司可以提供 110G~130GHz 的 IP 核,Keysight 公司在高精度示波器里用到了單片 40GHz 采樣率、10bit 的 ADC芯片,以及 Keysight 公司在高帶寬任意波發生器里用到了 92GHz 采樣率、8bit 的 DAC 芯片等。這些專用的芯片通常用于特殊應用,比如光通信或者高端儀表等,比較難以單獨獲得。

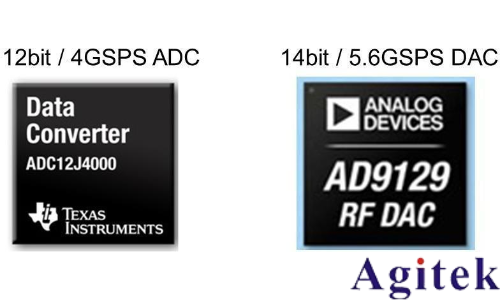

在商用領域,很多 ADC/DAC 芯片的采樣率也都已經達到了 GHz 以上,比如 TI 公司的 ADC 12J4000 是 4 GHz 采樣率、12bit 分辨率的高速 ADC芯片;而 ADI 公司的 AD9129 是 5.6 GHz 采樣率、14 bit 分辨率的高速 DAC 芯片。這一方面要求 ADC 有比較高的采樣率以采集高帶寬的輸入信號,另一方面又要有比較高的位數以分辨細微的變化。

隨著 ADC/DAC 的采樣率的提高,高速 ADC/DAC 的數字側的接口技術也在發生著比較大的變化。

低速串行接口:很多低速的 ADC/DAC 芯片采用 I2C 或 SPI 等低速串行總線把多路并行的數字信號復用到幾根串行線上進行傳輸。由于 I2C 或 SPI 總線的傳輸速度大部分在10Mbps 以下,所以這種接口主要適用于MHz 以下采樣率的ADC/DAC 芯片。

并行 LVCMOS 或 LVDS 接口:對于幾 MHz 甚至幾百 MHz 采樣率的芯片來說,由于信號復用后數據速率太高,所以基本上采用并行的數據傳輸方式,即每位分辨率對應 1 根數據線(比如 14 位的 ADC芯片就采用 14 根數據線),然后這些數據線共用 1 根時鐘線進行信號傳輸。這種方法的好處是接口時序比較簡單, 但是由于每 1 位分辨率就要占用 1 根數據線,所以占用芯片管腳較多。

JESD204B 串行接口:對于更高速率的 ADC/DAC芯片來說,由于采樣時鐘頻率更高,時序裕量更小,采用并行 LVCMOS 或 LVDS 接口的布線難度很大,而且占用的布線空間較大。為了解決這個問題,目前更高速和小型化的ADC/DAC 芯片都開始采用串行的JESD204B 接口。JESD204B 接口是把多位要傳輸的數據合并到一對或幾對差分線上,同時采用現在成熟的 Serdes(串行-解串行)技術用數據幀的方式進行信號傳輸,每對差分線都有獨立的 8b/10b 編碼和時鐘恢復電路。采用這種方法有幾個好處:首先數據傳輸速率更高,每對差分線按現在的標準最高可以實現 12.5 Gbps 的信號傳輸,可以用更少的線對實現高速數據傳輸;其次各對線不再共用采樣時鐘,這樣對于各對差分線間等長的要求大大放寬;借用現代 Serdes 芯片的預加重和均衡技術可以實現更遠距離的信號傳輸,甚至可以直接把數據直接調制到光上進行遠距離傳輸;可以靈活更換芯片,通過調整JESD204B 接口里的幀格式,同一組數字接口可以支持不同采樣率或分辨率的ADC芯片,方便了系統更新升級。

ADC主要性能指標分為靜態和動態兩部分:

主要靜態指標:

Differential Non-Linearity (DNL)

Integral Non-Linearity (INL)

Offset Error

主要動態指標:

Total harmonic distortion (THD)

Signal-to-noise plus distortion (SINAD)

Effective Number of Bits (ENOB)

Signal-to-noise ratio (SNR)

Spurious free dynamic range (SFDR)

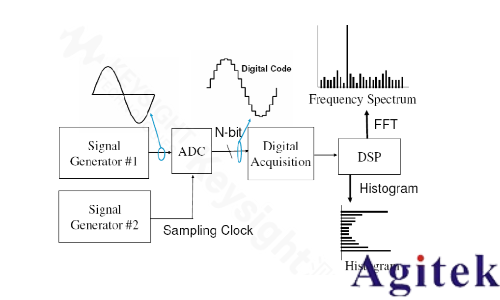

要進行 ADC這些眾多指標的驗證,可用的方法很多。最常用的方法是給 ADC 的輸入端提供一個理想的正弦波信號,然后對 ADC 對這個信號采樣后的數據進行采集和分析。因此,ADC性能測試需要多臺儀器的配合并用ADC軟件對測試結果進行分析。下圖是最常用的進行ADC性能測試的方法。

在測試過程中,第 1 個信號發生器用于產生正弦波被測信號,第 2 個信號發生器用于產生采樣時鐘,采樣后的數字信號經 FFT 處理進行頻譜分析和計算得到動態指標,經過直方圖統計得到靜態指標。

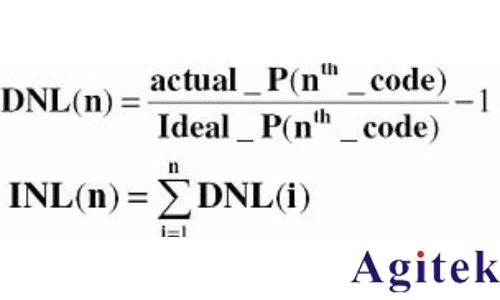

靜態指標是對正弦波的采樣數據進行幅度分布的直方圖統計,然后間接計算得到。如下圖所示,理想正想波的幅度分布應該是左面的形狀,由于非線性等的影響,分布可能會變成右邊的形狀,通過對實際直方圖和理想直方圖的對比計, 可以得出靜態參數的指標。

以下是 DNL 和 INL 的計算公式:

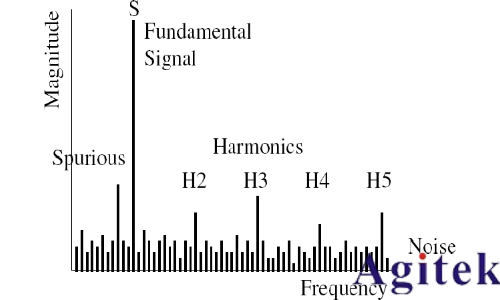

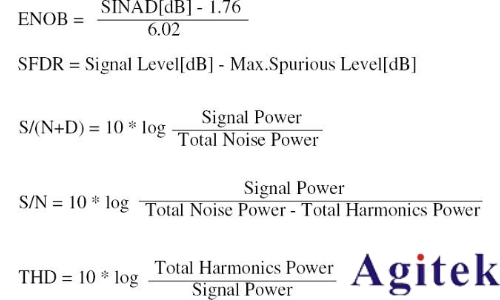

動態指標是對正弦波的采樣數據進行 FFT 頻譜分析,然后計算頻域的失真間接得到。一個理想的正弦波經 A/D 采樣,再做后頻譜分析可能會變成如下圖的形狀。除了主信號以外,由于ADC芯片的噪聲和失真,在頻譜上還額外產生了很多噪聲、諧波和雜散,通過對這些分量的運算,可以得到ADC動態參數。

通過 FFT頻譜分析測試動態參數

下面是動態參數的計算公式:

對于產生被測信號和采樣時鐘的信號發生器來說,為了得到比較理想的測試效果, 要求其時間抖動(或者相位噪聲)性能要足夠小,因為采樣時鐘的抖動會造成采樣 位置的偏差,而采樣位置的偏差會帶來采樣幅度的偏差,從而帶來額外的噪聲,從 而制約信噪比的測量結果。下圖是時鐘或者信號抖動引起信噪比惡化的示意圖,以 及根據信噪比要求及輸入信號頻率計算信號抖動要求的公式。

技術支持

關注官方微信

關注官方微信